## Imperial College London

## Lecture 16 (Supplementary)

## spi2dac.v Explained

Peter Cheung

Department of Electrical & Electronic Engineering

Imperial College London

URL: www.ee.imperial.ac.uk/pcheung/teaching/E2\_CAS/E-mail: p.cheung@imperial.ac.uk

PYKC 2 Dec 2025 EE2 Circuits and Systems Lecture 16 Slide 1

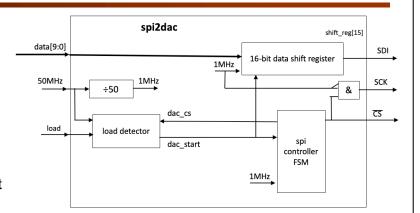

## Spi2dac.v design overview

- The components inside spi2dac are:

- Clock divider

- 2. Load detector to detect load pulse

- 3. FSM to control the spi interface

- Parallel to serial shift register to shift OUT the command and data to the DAC

- Various gates e.g. inverters and AND gates

- Note that the Verilog code is designed to match the block diagram shown here

- It consists of TWO state machines, a counter and a shift register

PYKC 2 Dec 2025 EE2 Circuits and Systems Lecture 16 Slide 2

In order to use the DAC, you have to include the interface module "spi2dac" in your design. This module has a schematic shown above. It takes two inputs (in addition to the 50MHz clock signal): data[9:0] is the 10-bit digital data to be converted by the DAC, and a load signal which is a high pulse to trigger the spi2dac module to send the 10-bit data to the DAC.

The internal working of sp2dac can be divided into 4 main modules. The divide-by-50 module is straight forward – it produces a 1MHz clock for the finite state machine, and is gated through the AND gate to generate the serial clock signal (at 1MHz).

The load detector module handles the load command and produces control signals to the SPI state machine and the shift register.

The shift register sends the control bits and the 10-bit data serially to the SDI output. The spi controller FSM is the main control module designed as a state machine.

We will now consider each sub-module individually.

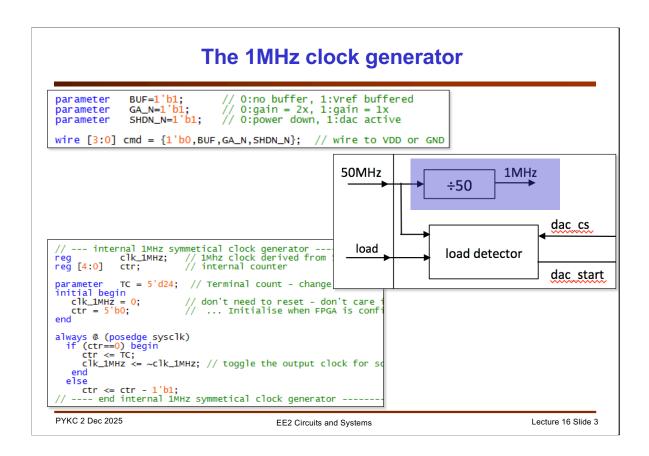

This is a straight forward clock divider. The Terminal Count (TC) is set to 24. Divide by 50 is done by toggling the output (clk\_1MHz) after 25 clock cycles. Note that I generally prefer to use a down-counter instead of an up-counter. The counter (ctr) is set to 24, it then counts to zero. Output is toggled and the counter (ctr) is reset to the initial value of 24 again.

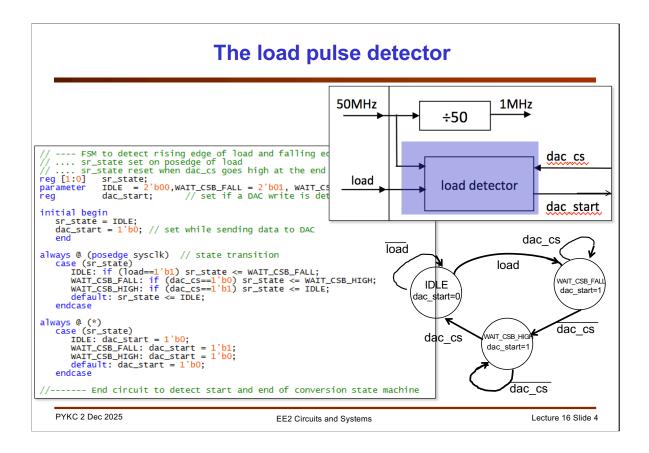

We have TWO signals to detect: the load pulse and the dac cs signal.

Starting in the IDLE state, when load signal is asserted, we start the DAC cycle by entering the WAIT\_CSB\_FALL state. In this state, dac\_start is asserted, and we wait for DAC\_CS to go low from the SPI controller circuit. In this condition, the DAC is in the middle of accepting a new data for conversion. We go to state WAIT\_CSB\_HIGH TO wait for the conversion to be completed, which is indicated by DAC\_CS going high. When that happens, we return to the IDLE state waiting for another 10-bit data to be loaded.

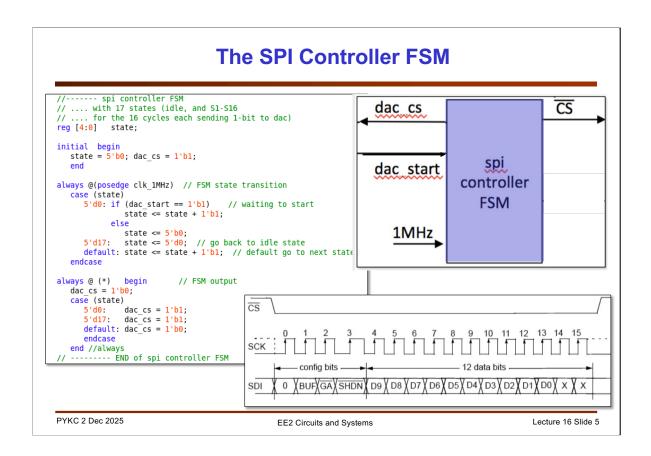

The controlling FSM controller is actually simpler than it first appears.

We need a FSM to have 18 states. State 0 is the idle state, waiting for a new data to be sent to the DAC. Here DAC\_CS (which is low active) is '1' and we wait for the dac\_start to be asserted.

The default value of dac\_cs and state are specified first. By default we always go to the next state, i.e. state value goes up by 1.

Once the state machine moves to state 1, it just go through to state 16, which corresponds to cycle 0 to 15 in the timing diagram here. At the end of state 16, we de-assert dac\_cs (i.e. go high), and go back to the IDLE state.

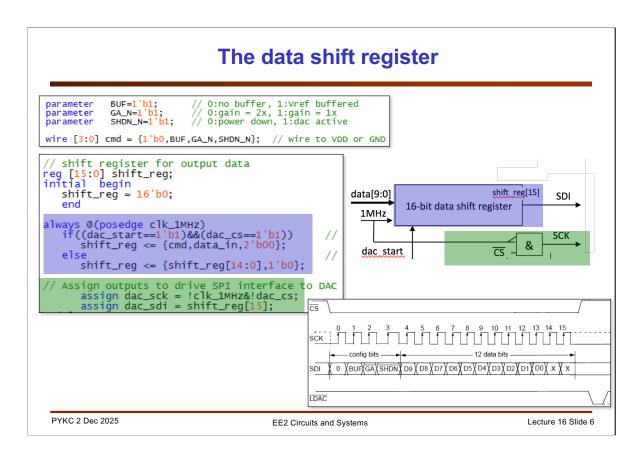

Finally, the data and clock output is specified here. SDI is driven through a parallel in, serial out shift register.

We use a number of useful tricks here:

1.cmd is a 4-bit value defining the first four bits of the SDI data values. We use symbolic variable names to make the code easy to read.

2.Shift\_reg <= {cmd, data\_in, 2'b00} - parallel load the 16-bit value into the shift register.

3.Shift\_reg <= {shift\_reg[14:0], 1'b0} - perform left shift

The SDI is taken from the MSB of the shift register. The serial clock Is !dac\_cs (low active) ANDed with the inverter version of the clock (making the rising edge of the SCK signal in the middle of the data bit).